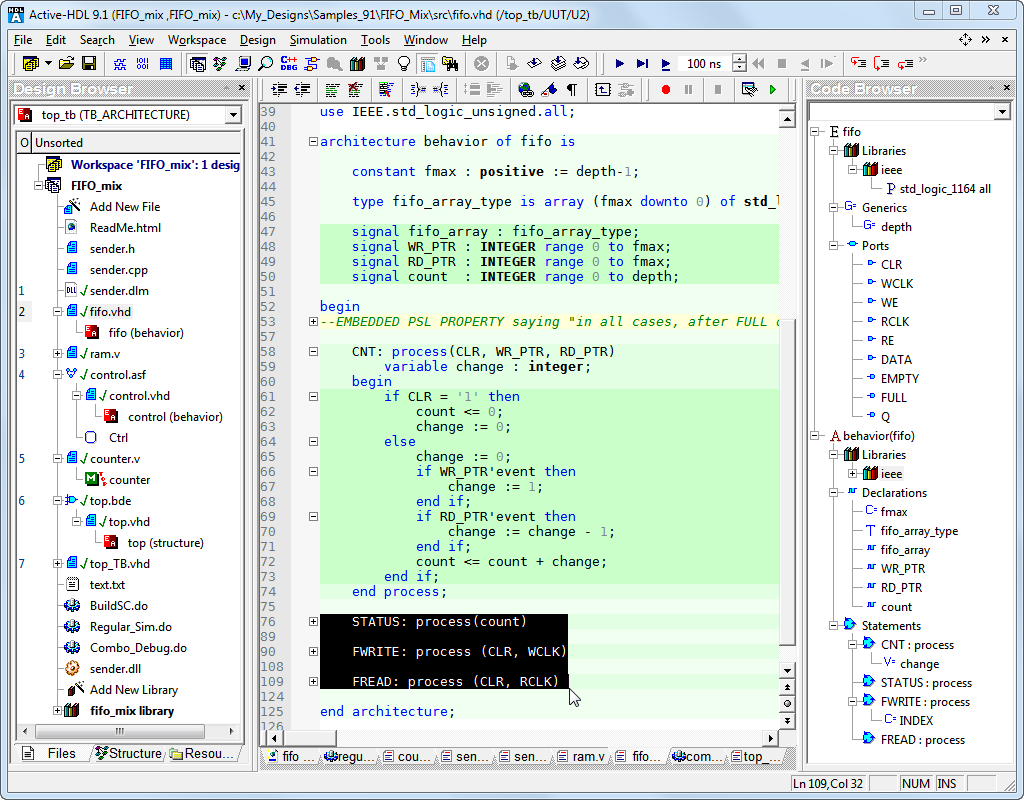

Active HDL’s Integrated Design Environment includes a complete HDL and graphic design tool suite as well as an RTL/gate-level mixed-language simulator for speedy deployment and validation of FPGA designs. Furthermore, the ability to simulate 64 bits is now available in default to a selection of most popular configurations, as well as improvements to Active-HDL’s state machine and block diagram editors. Get More Softwares From Getintopc

Password 123

Active Hdl

The first method relies on consecutive clicks, while the second one requires you to keep your mouse in place while drawing. This is the preferred option for designers who work with large quantities of data from simulations. It is designed to be optimized for large-scale designs and lengthy simulation runs.

Active Hdl Features

Select the top-level category, and select the top-level device from the available design models. Move the mouse pointer towards the point you wish to begin drawing the wire, then press your mouse’s button. Move the mouse pointer towards the location where you wish to finish the wire. If you move the mouse pointer the wire will be stretched between the wire’s beginning and the current position that the pointer is located.

It can, for instance, illustrate that the current simulation has overwritten the results from the previous that you ran and lets you make use of hotkey stimulators. If you are running the simulation without a top-level unit, Active-HDL will provide you with a dialogue box asking you to choose one. Sign up or log into the Aldec support account by going to http://support.aldec.com/ to start a support case or download the program.

If you would like to finish the wire within a blank diagram space, you need to double-click instead click. Click anywhere in the diagram to deactivate the change to the arrow. Move your mouse towards the upper part of the and choose the location you would like to place the port.

Students can use Active-HDL as their student Edition is a mixed-language design entry and simulation tool that is provided for free through Aldec Students can utilize it in their studies. A saved macro file can later be used to add signals to the waveform to run another simulation run. This macro can be executed within your script as soon as you’ve started your simulation. You can restart the simulation to restart simulation, without losing any signals from the waveform. Menu Only VHDL files are reordered. There are two ways of drawing wires.

Click inside the state bubble where the transition is over. It will be visible and the mouse will take on the usual shape of the selection. To define a variable, place the mouse’s pointer within the frame of the machine and then select the location where you wish to put the symbol for the variable or signal.

How to Get Active Hdl for Free

The command starts the elaboration process and initiates the model simulation. When elaboration is completed, the simulator loads design elements and creates the simulation model into the memory of the computer. In the process of the initialization process, all objects within the model (signals and variables.) get their initial values, and every concurrent process is executed one time until they cease.

Select the design’s name and choose the location of the design folder. Its name for the default library for the design is the same as the name of the design. The Active HDL Installshield program has been improved to support 4K screens. In addition, the tool’s GUI has been updated and menus have been updated along with new dialog boxes and icons. It is better suited to work using small-sized designs, especially when using the interactive mode.

In this video, we will use the example VHDL design called PressController that is part of the Active-HDL installation for designing entry as well as simulation. The compilation is studying the source file. Design units that are analyzed in the file are inserted inside the library of working in a form that is readable for the software.

In Active-HDL, the source file could be a VHDL Verilog file/EDIF netlist file or State diagram file and Block diagram files. Active-HDL can be used with the top FPGA devices such as Intel(r), Lattice(r), Microsemi(tm), Quicklogic(r), Xilinx(r), and many more. Active-HDL(tm) is a Windows(r) powered that integrates FPGA Design Creation and Simulation solution for teams working in collaborative environments.

Active Hdl System Requirements

- Operating System: Windows XP/Vista/7/8/8.1/10

- RAM: 1 GB

- Hard Disk: 600 MB

- Processor: Intel Pentium IV or higher processor